Peter Hofbauer’s private Homepage

Selbstbauprojekte

eigene Entwicklungen

HF-Meßplatz mit Spektrumanalyzer, Meßsender, Wobbler und HF-Voltmeter , Seite 3/7

Der Schaltplan, Beschreibung (2)

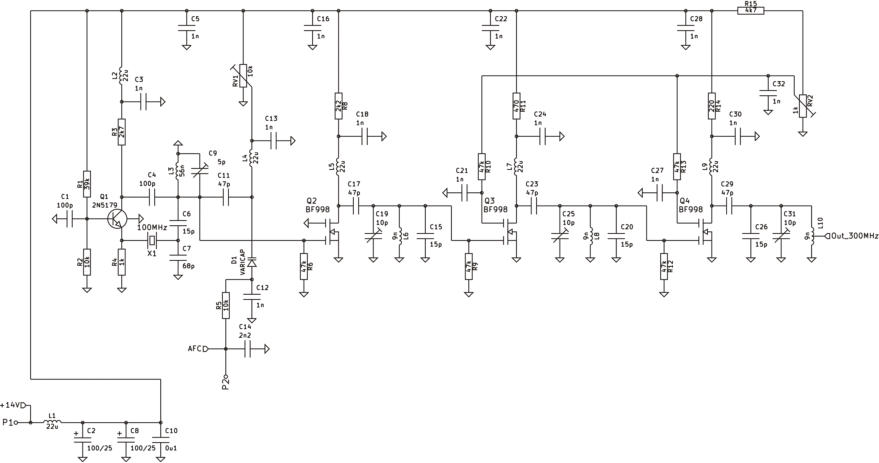

7.) die beiden 300MHz-Oszillatoren

“VCO#2”, Datei HFP9500C und “VCO#3”, Datei HFP9500H

Die Schaltung der beiden Oszillatoren sind identisch. Die 300MHz müssen aus einen 100MHz-Quarz-Oszillator durch Verdreifachung erzeugt

werden. Der Quarzoszillator kann mit einer Varicap verändert werden. Dadurch ist die Frequenz zwischen 199,99828MHz und 199,99777MHz

einstellbar.

Der 100MHz-Quarzoszillator mit 2N5179 arbeitet sehr schwingfreudig. Der Quarz schwingt in der 5. Oberwelle. Der Kreis L3/C9 plus der übrigen

Kapazitäten ist auf 100MHz abgestimmt. Trimmpoti RV1 wird so eingestellt, das die Stellspannung an “AFC” von 0 bis 5V geht.

Die Stufe mit Q2 (BF998) arbeitet mit geringen Drainstrom um möglichst stark zu verzerren. Darauf folgen zwei auf 300MHz abgeglichen Stufen.

Insgesamt wird mit drei Parallelkreisen die 300MHz aus den Spektrum gefiltert. Dieser hohe Aufwand ist auch nötig. Die vorherigen Versionen,

diese Schlatung ist die vierte Version, hatten noch zu viele 100MHz-Oberwellen neben 300MHz am Ausgang.

Mit Trimmpoti RV2 wird die erforderliche Pegel eingestellt. Der VCO#2 soll 7dBm liefern, der VCO#3 dagegen nur etwa -3dBm.

Diese Oszillatoren sind in SMD-Technik aufgebaut.

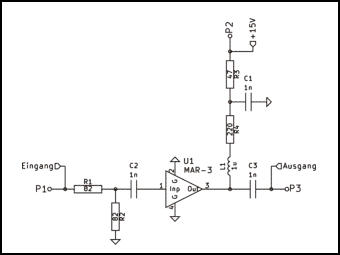

8.) Trennstufe

“Trennstufe”, Datei HFP9500B3

Diese Stufe habe ich nachträglich einbauen müssen. Sie dient der Entkopplung. Die HF

vom VCO#3 gelangte über VCO#1 zum Mischer#1. Das führte zu falschen Signalen im

Spektrum.

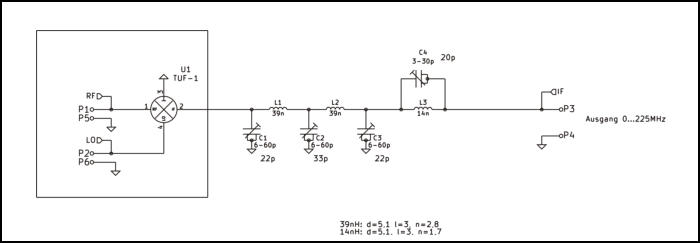

9.) Mischer für den Meßsender

“Mischer#3”, Datei HFP9500J

In dieser Mischstufe mit

Ringmischer TUF-1 wird die

Frequenz für den Meßsender

erzeugt. Am Ausgang folgt ein

240MHz-Tiefpass und mit L3/C4

eine 300MHz-Sperre.

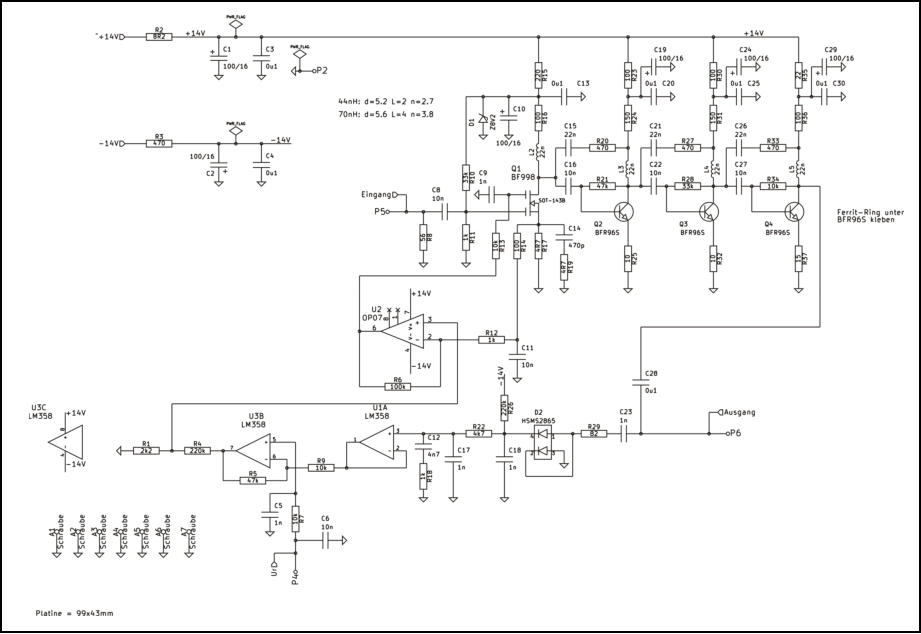

10.) Verstärker und Modulator für den Meßsender

“Modulator”, Datei HFP9500F

Diese Schaltung ist die einzige, die nicht geändert werden mußte. Die HF vom Mischer#3 wird mit den Dualgate-FET Q1 (BF998) in der

Amplitude geregelt. Damit dies mit möglichst geringen Verzerrungen erfolgt, darf diese Stufe nur mit kleinen Pegeln arbeiten. Darauf folgen

drei Breitband-Verstärker mit BFR96S. Diese Transistoren neigen oft zum Schwingen. Vor allem wenn in der Emitterleitung noch ein

Widerstand liegt. Auch hier konnte ich ein Schwingen erkennen. Kleine Ferritringe wurden auf den Transistor geklebt und der Spuk war vorbei.

Die Ausgangsspannung soll über den kompletten Bereich von 100kHz bis 245MHz konstant bleiben. Dafür soll eine Regelschaltung sorgen.

Die Ausgangsspannung wird mit D2 (HSMS2865) gleichgerichtet und mit U1A niederohmig gemacht. Der U3B vergleicht diese Spannung mit

der Sollspannung an P4 (Ur). Diese kommt von einen DAC auf der CPU-Platine. Der Spannungsteiler R4/R1 vermeidet Übersteuerung. Der U2

(OP07) stellt den Drainstrom proportional zur Spannung zwischen R1 und R4 ein. Dadurch wird die Regelkurve des BF998 einigermaßen

linear.

Die CPU kann mit dieser Schaltung die Amplitude einstellen und modulieren. Die Schleifenverstärkung in dieser Regelung konnte leider nicht

höher eingestellt werden. Aus Gründen der Stabilität. Eine restliche Schwankung der Ausgangspegel um etwa 3dB bleibt und wurde mit einer

Korrekturtabelle in der Software beseitigt.

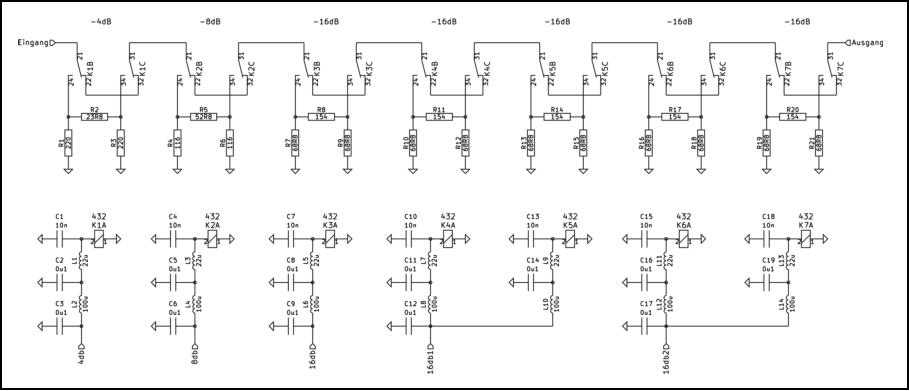

11.) Der Eichteiler des Meßsenders

“Eichteiler”, Datei HFP9500K

Am Ausgang des Meßsender-Verstärkers folgt der Eichteiler. Der besteht aus 7 hintereinder geschaltete Pi-Abschwächern. Insgesamt kann der

Pegel in 1dB-Schritte von 0 bis 91dB abgeschwächt werden. Die 1dB und 2dB (und damit auch 3dB) -Abschwächung erfolgt mit Hilfe des

Reglers im Meßsender-Verstärker, die 4dB, 8dB und fünf mal 16dB sind als Widerstandsschaltung mit HF-Relais verwirklicht.

Der Breitbandverstärker ist mit den Eichteiler in ein Gehäuse, das ich aus einen Aluminiumblock heraus gefräst habe.

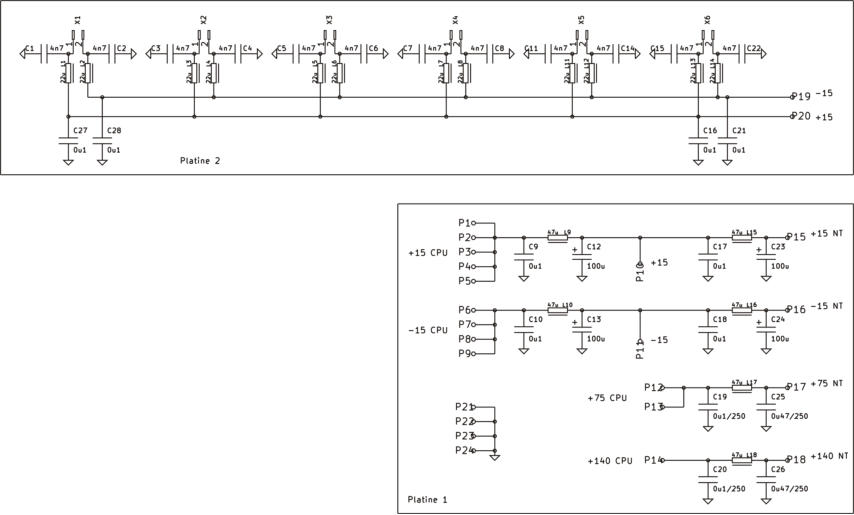

12.) Die Spannungsversorgung

“Spannungsfilter”, Datei HFP9500P

Der originale Teil im alten Tektronikgehäuse liefert insgesamt 4 stabilisierte Spannungen:

+15V, -15V, +75V und +140V.

Alle Spannungen werden mit 2 Platinen im HF-Teil gegen Störspannungen aufwändig gesiebt. Ob die alle nötig waren, habe ich allerdings nicht

getestet. Dazu hätte ich die Platinen versuchsweise wieder ausbauen müssen.

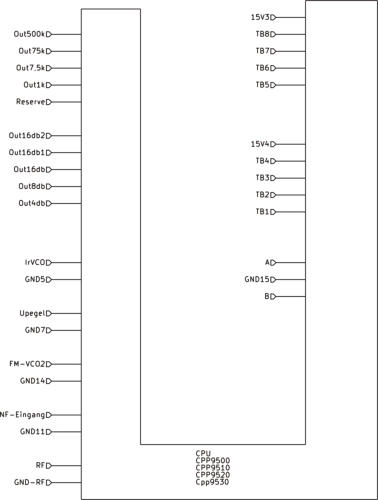

13.) Die CPU-Platine

“CPU”, Datei HFP9500CPU

Im Übersichts-Schaltplan sind im CPU-Teil nur die Anschlüsse gezeichnet.

Die CPU-Plaine(n) steuern den HF-Teil mit folgenden Anschlüssen:

4 digitale Ausgänge mit etwa 14V für die Relais auf der Baugruppe “Filter”

1 digitaler Ausgang, (”Reserve”) über Spannungsteiler zur Triggerausgangsbuchse

5 digitale Ausgänge mit etwa 14V für die Relais im “Eichteiler”

1 digitaler Ausgang einstellbar bis 5V für die “AFC” des VCO#2

1 analoger Eingang für die Meßspannung

1 analoger Ausgang etwa 1 bis 4V für die Pegelsteuerung des Meßsenders

1 Impuls-Stromausgang für die PLL-Steuerung des VCO#1

1 HF-Eingang vom VCO#1 für die PLL

und für die Bedienung:

8 digitale Eingänge für die Tasten

2 digitale Eingänge für den Inkrementalgeber

Die CPU-Platine besteht eigentlich aus 4 getrennte Platinen:

CPP9500 = die eignetliche CPU-Platine mit einen ATMEGA

CPP9510 = Die PLL-Schaltung mit zusätzlich den DDS-Modul

CPP9520 = die Ablenkverstärker für die Oszilloskopröhre

CPP9530 = der schmale Tastenprint

In der folgenden Seite werden die Schaltungen der CPU-Platinen im Detail beschrieben.

Diese Platine siebt die Spannungen für die HF-Baugruppen

Diese Platine sitzt zwischen

Tek.Netzteil und meiner Konstruktion